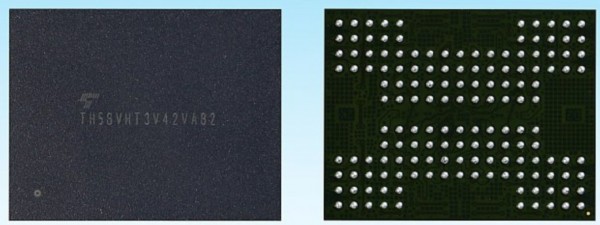

硬件发烧友们一直期待着更快、更实惠、更可靠的存储产品,而大型数据中心则更关注与能源效率。本文要为大家介绍的,就是东芝 BiCS 3D TLC NAND 闪存所使用的硅穿孔(TSV)技术。其声称可减少存储应用的功耗,同时保障低延时、高吞吐、以及企业级 SSD 的每瓦特高 IOPS 。据外媒所述,这是当前业内首个推向市场的硅穿孔 NAND 闪存产品。

TSV 是指垂直通过硅芯片的电气连接,东芝称这种制造方法有助于提升能源效率和带宽。与当前基于键合(wire-bonding)技术的闪存芯片相比,TSV BiCS 闪存芯片可带来两倍能效。

它将堆叠的核心引脚连接了起来,尽管增加了一定的制造复杂度和成本,但最终价格还是可以比其它形式的 NAND 要便宜一些。目前 TSV 人多用于堆栈式 DRAM,比如 AMD 在 Fuji 和 Vega 高端桌面级显卡上所采用的 HBM 闪存。

东芝初期将提供 512GB 和 1TB 容量、以及 1066 Mbps 的 TSV NAND 产品,大小为 14×18 mm 。八层 512GB 芯片的厚度为 1.35 mm,而 16 层 1TB 的芯片厚度为 1.85 mm 。

该公司称,它已于上月向制造合作伙伴出货基于 TSV 技术的 BiCS 3D TLC 闪存芯片,预计样品可在年底前出货。此外东芝也将于 8 月第二周在圣克拉拉举办的“2017 闪存峰会上”展示相关原型。

京公网安备 11010502049343号

京公网安备 11010502049343号